# KODAK CCD PRIMER

# #KCP-001

# CHARGE-COUPLED DEVICE (CCD) IMAGE SENSORS

This primer is intended for those involved with CCD image sensing applications who wish to obtain additional insight into the mechanisms of CCD sensor principles and operations. It is not intended to provide an exhaustive study into the detailed theory behind the subject and it is assumed that a silicon based CCD is used unless otherwise stated. It is also assumed that a conventional front illuminated detector system is employed. Some references are listed at the conclusion.

# I Introduction

Like many technologies, the Charge-Coupled Device (CCD) started out as one kind of creature and wound up as something completely different. Invented in the late 1960's by researchers at Bell Labs, it was initially conceived as a new type of computer memory circuit, and it was demonstrated in 1970 for that facility. It soon became apparent that the CCD had many other potential applications, including signal processing and imaging, the latter because of silicon's light sensitivity which responds to wavelengths less than 1.1µm (the visible spectrum falls between 0.4µm and 0.7µm). The CCD's early promise as a memory element has since disappeared, but its superb ability to detect light has turned the CCD into the premier image sensor technology.

Like integrated circuits (IC), CCD's begin on thin wafers of silicon which are processed with a series of elaborate steps which define the various functions within the circuit. On each wafer lies several identical devices (die), each capable of yielding a functional device. Selected die, based on a variety of preliminary screening tests, are then cut from the wafer and packaged into a carrier for use in a system.

The scope of this primer is to introduce the reader to the basics of CCD imaging. The gualitative discussions described herein reflect silicon based imaging applications in the visible spectrum.

# **II CCD** Formats

Image sensing can be performed using three basic techniques: point scanning, line scanning and area scanning. CCD's, by their definition, can take the form of line and area scanning formats.

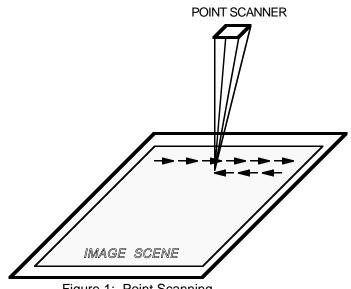

#### **Point Scanning** A)

Using a single cell detector or pixel (picture element), an image can be scanned by sequentially detecting scene information at discrete XY coordinates. Advantages to this approach are high resolution, uniformity of measurement from one site to another and the cost/simplicity of the detector. Disadvantages include registration errors from the XY movement of scene or detector, frame scanning rates because of the repeated number of exposures and system complexity due to the XY movement.

Figure 1: Point Scanning

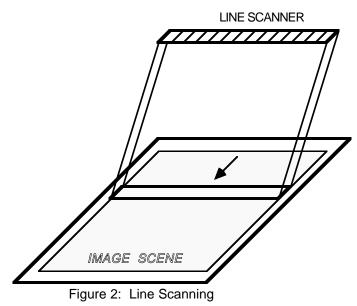

#### B) Line Scanning

An array of single cell detectors can be placed along a single axis such that scanning now takes place in only one direction. In this case, a line of information from the scene is captured and subsequently readout of the device before stepping to the next line index. The physical length of a linear CCD scanner is only limited by the size of the starting silicon wafer used to fabricate the device. This limitation is sometimes overcome (with significant additional complexities and costs) by mounting several linear CCD's end to end to increase the overall length. Line scanning greatly improves the scan time over point scanning. Other benefits include reasonably high resolution and less sophisticated scanning mechanics. However, resolution is limited by the pixel spacing and size in the one direction. Measurement accuracy at each pixel has finite nonuniformities which occasionally must be factored out with the system. Scan times, of the order of several seconds or minutes, are still unsuitable for many applications and the costs of linear CCD's are considerably more expensive than single cell detectors. Costs are dictated by the finite number of CCD's one can place on each wafer and the resulting yield loss from processing errors.

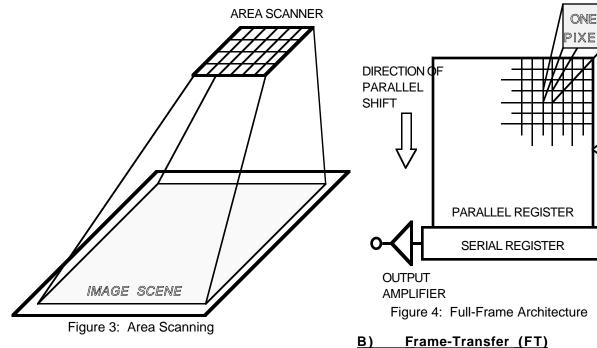

# C) Area Scanning

A two dimensional array of detectors can be created such that the entire image can be captured with one exposure eliminating the need for any movement by detector or scene. Area scanners are capable of producing the highest frame rates with the greatest amount of registration accuracy between pixels. System complexities are also kept to a minimum. However, resolution is now limited in two directions. Other disadvantages include generally lower signal-tonoise performance and cost because fewer devices can be placed on a wafer and yield is inherently lower for a number of reasons.

# **III CCD Architectures**

CCD's can take on various architectures. The primary CCD's in use today are called Full-Frame Transfer and Frame-Transfer devices, which use MOS photocapacitors as detectors and Interline Transfer devices which use photodiodes and photocapacitors as the detector. Each is described below as applied to area CCD sensors but the concepts apply to linear CCD's as well. Other image sensing architectures, which will not be discussed here, include Frame-Interline Transfer, Accordian, Charge Injection and MOS XY addressable among others.

# A) Full-Frame (FF)

FF CCD's have the simplest architecture and are the easiest to fabricate and operate. They consist of a parallel CCD shift register, a serial CCD shift register and an signal sensing output amplifier. Images are optically projected onto the parallel array which acts as The device takes the scene the image plane. information and partitions the image into discrete elements which are defined by the number of pixels thus "quantizing" the scene. The resulting rows of scene information are then shifted in a parallel fashion to the serial register which subsequently shifts the row of information to the output as a serial stream of data. The process repeats until all rows are transferred off chip. The image is then reconstructed as dictated by the system. Because the parallel register is used for both scene detection and readout, a mechanical shutter or synchronized strobe illumination must be used to preserve scene integrity. The simplicity of the FF design yields CCD imagers with the highest resolution and highest density.

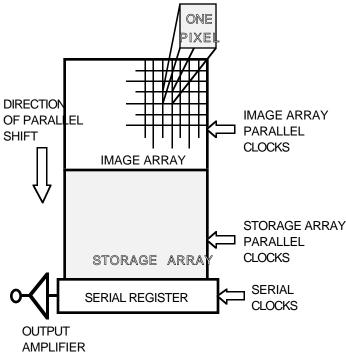

FT CCD's are very much like FF architectures. The difference is that a separate and identical parallel register, called a storage array, is added which is not

PARALLEL CLOCKS

SERIAL

CLOCKS

light sensitive. The idea is to shift a captured scene from the photosensitive, or image array, very quickly to the storage array. Readout off chip from the storage register is then performed as described in the FF device previously while the storage array is integrating the next frame. The advantage of this architecture is that a continuous or shutterless/strobeless operation is achieved resulting in faster frame rates. The resulting performance is compromised, however, because integration is still occurring during the image dump to the storage array which results in image "smear". Because twice the silicon area is required to implement this architecture, FT CCD's have lower resolutions and much higher costs than FF CCD's.

Figure 5: Frame-Transfer Architecture

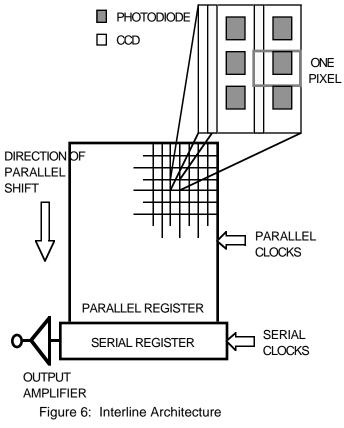

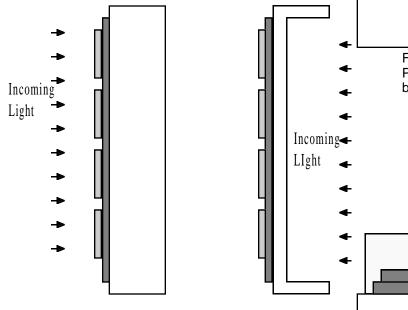

# <u>C)</u> Interline (IL)

IL CCD's are incorporated to address the shortcomings of the FT devices. This is achieved by separating the photo-detecting and readout functions by forming isolated photosensitive regions in between lines of non-sensitive or light shielded parallel readout CCD's. After integrating a scene, the signal collected in every pixel is transferred, all at once, into the light shielded parallel CCD. Transfer to the output is then carried out similar to FF and FT CCD's. During readout, like the FT CCD, the next frame is being integrated thus achieving a continuous operation and a higher frame rate. Because of this architecture, the image smear during readout using FT CCD's is significantly improved using The major disadvantages of IL CCD IL CCD's. architectures is their complexity which leads to higher unit costs and lower sensitivity. Lower sensitivity occurs because less photosensitive area (ie a reduced aperture) is present at each pixel site due to the associated light shielded readout CCD. Furthermore,

quantization (or sampling) errors are greater because of the reduced aperture. Lastly, some IL architectures using photodiodes suffer image "lag" as a consequence of charge transfer from photodiode to CCD.

# IV CCD Basics

CCD imaging is performed in a three step process: (1) exposure which converts light into an electronic charge at discrete sites called pixels, (2) charge transfer which moves the packets of charge within the silicon substrate and (3) charge to voltage conversion and output amplification.

#### <u>A) Converting Light (Photons) to Electronic</u> Charge

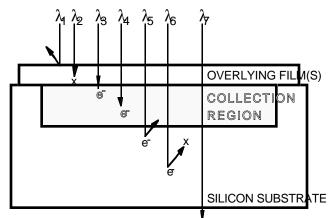

An image is acquired when incident light, in the form of photons, falls on the array of pixels. The energy associated with each photon is absorbed by the silicon which causes a reaction to take place. This reaction yields the creation of an electron-hole charge pair (or simply an electron). The number of electrons collected at each pixel is linearly dependent on light level and exposure time and non-linearly dependent on wavelength. Many factors can affect the ability to detect a photon. Thin films of materials intentionally grown and deposited on the surface of the silicon during fabrication can have a tendency to absorb or reflect the light as in the photo-capacitor's case. Photons are absorbed at different depths in the silicon depending on their wavelength. There are instances in which photon induced electrons cannot be detected because of the location within the silicon where they were created.

Figure 7: Photon Interaction with Silicon

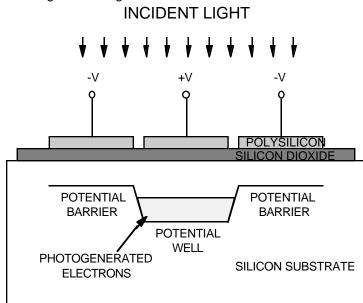

# **B)** Potential Wells and Barriers

CCD's follow the principles of basic Metal Oxide Semiconductor (MOS) device physics. A CCD MOS structure simply consists of a vertically stacked conductive material (doped polysilicon) overlying a semiconductor (silicon) separated by a highly insulating material (silicon dioxide). By applying a voltage potential to the polysilicon or "gate" electrode, the electrostatic potentials within the silicon can be changed. With an appropriate voltage a potential "well" can be formed which has the capability of collecting the localized electrons that were created by the incident light. The electrons can be confined under this gate by forming zones of higher potentials, called barriers, surrounding the well. Depending on the voltage, each gate can be biased to form a potential well or a barrier to the integrated charge.

Figure 8: Potential Well and Barrier

### C) Charge Transfer Techniques

Once charge has been integrated and held locally by the bounds of the pixel architecture, one must now have a means of getting that charge to the sense amplifier which is physically separated from the pixels. The common methods used today involve four differing charge transfer techniques which are described below. One thing to keep in mind as we walk through these techniques is that as we move the charge associated with one pixel, we are at the same time moving all the pixels associated with that row or column.

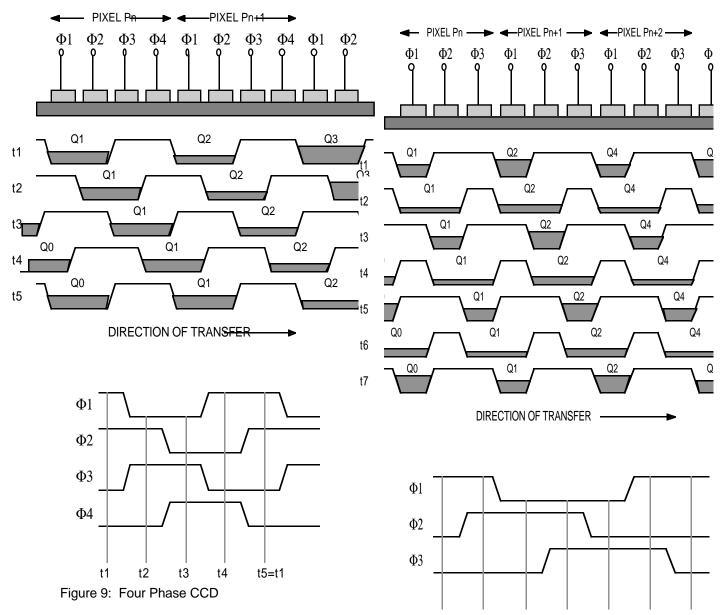

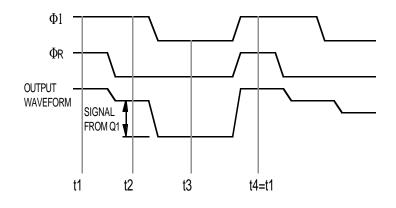

> 1) Four Phase (4 $\Phi$ ) CCD - CCD shift registers are formed by defining polysilicon electrodes such that they form a long chain of gates along one axis forming a column. If one applies a high level voltage to one of these gates, a potential well is formed beneath that gate while a low level voltage forms a potential barrier. Four gates are used to define a single pixel. As the timing diagram shows during integration, if we hold the voltage on the  $\Phi$ 1 and  $\Phi 2$  gates high while keeping the voltage at the low level on the  $\Phi$ 3 and  $\Phi$ 4 gates, we can form a potential well which integrates and collects photo-induced charge for pixel Pn. If  $\Phi$ 1 and  $\Phi$ 3 then change their polarity (ie  $\Phi$ 1 goes from high to low and  $\Phi 2$  goes from low to high) the charge packet is forced by electrostatics to move beneath  $\Phi 2$  and  $\Phi 3$ .  $\Phi 2$  and  $\Phi 4$  now reverse their polarity and the charge is moved further now occupying the well formed by the  $\Phi$ 3 and  $\Phi$ 4 electrode. This process is carried out until the charge packet lies beneath the 1 and 2 gates of the next pixel  $p_{n+1}$  which now completes one transfer cycle. The cycle is repeated until all charge packets have reached the output. Thus we use 4 gates per pixel.

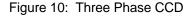

2) Three Phase (3 $\Phi$ ) CCD - 3 $\Phi$  CCD's are similar to  $4\Phi$  CCD's except that the number of barrier biased gates separating the well biased electrodes is reduced from  $\Phi 2$  to  $\Phi 1$  while the timing requirements change slightly. In this technique, charge is residing under  $\Phi$ 1 while  $\Phi 2$  and  $\Phi 3$  are held in the barrier state.  $\Phi 2$  is then brought to the high level followed shortly by  $\Phi$ 1 assuming the low level. The charge, now residing under the  $\Phi 2$  gate be shifted under the  $\Phi$ 3 gate by manipulating  $\Phi$ 2 and  $\Phi$ 3 in the same manner as described above. The transfer cycle completes when the charge is shifted to the  $\Phi$ 1 gate of the next pixel. The advantage of this operation is that only three gates are required to define a pixel thus allowing for higher density (and higher resolution) CCD's. The disadvantage of  $3\Phi$ over  $4\Phi$  is that more elaborate clocking must be generated to drive the device.

t3

t5

t4

t6

t7=t1

t2

t1

3) Pseudo Two Phase (P2 $\Phi$ ) CCD -P2 $\Phi$  CCD's mimic a 4 $\Phi$  operation except that now only two phase clocks are required to implement the transfer procedure. As shown below, each phase is tied to two gates instead of one. To assure that pixels are not mixed during the transfer operation, alternate gates are processed such that the electrostatic potentials occur at different levels for a given gate bias. Once this is achieved, proper transfer can occur using only two phases thus reducing the complexity required for driving the CCD. The expense one pays for this advantage is that extra processing is required adding cost to the device.

Figure 11: Pseudo Two Phase CCD

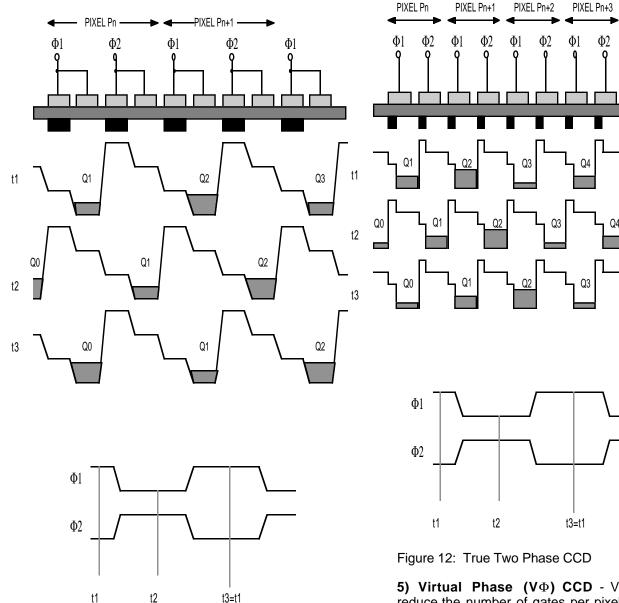

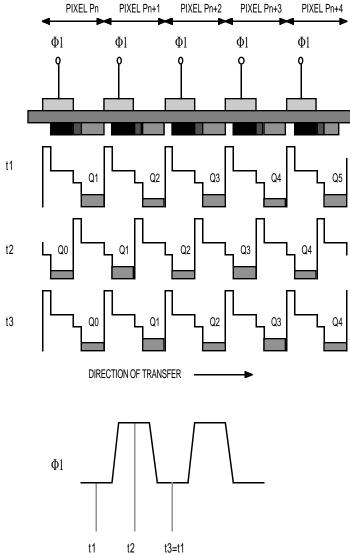

4) True Two Phase  $(T2\Phi)$  CCD -  $T2\Phi$ reduces the number of gates per pixel and the number of CCD drive phases to only two as shown below. This is achieved by creating the stepped potential beneath each gate as contrasted with the P2 $\Phi$  wherein two adjacent gates are required to form the stepped potnetial. T2 $\Phi$  is clocked just like P2 $\Phi$  shown earlier except that T2 $\Phi$  technologies have the capacity for very high densities and very high resolutions. The disadvantage is that the processing becomes more extensive thus adding costs. 5) Virtual Phase (V $\Phi$ ) CCD - V $\Phi$  CCDs reduce the number of gates per pixel and the number of CCD drive phases to only one as shown below. Characteristic to  $V\Phi$  CCDs is the absence of any polysilicon electrodes between the  $\Phi$ 1 gates. This makes the V $\Phi$ CCD inherently more sensitive to light (especially in the blue) because of the reduced overlying topography which could absorb or reflect the light. Charge transfer efficiency is preserved by creating a stepped and "pinned" potential within the silicon. High pixel densities are achievable with this architecture also. Some disadvantages are the high clock swings required by  $\Phi 1$  and some yet unresolved performance degradations presumably due to the multiple implant complexities.

PIXEL Pn+4

Φ2

Φ1

Figure 13: Virtual Phase CCD

# D) Readout Techniques

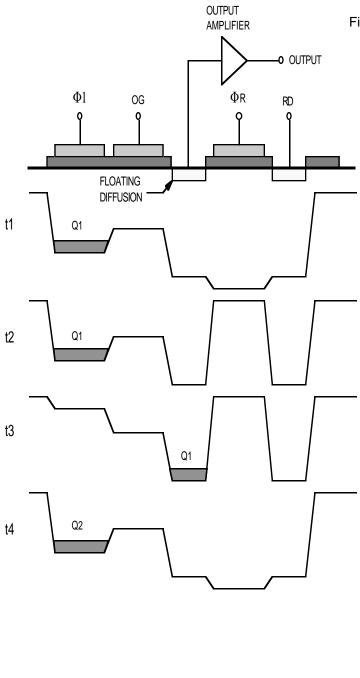

The packets of charge are eventually shifted to the output sense node where the electrons (which represent a charge) are converted to a voltage which is easier to work with off chip. Conventional techniques usually employ a floating diffusion sense node followed by a charge to voltage amplifier such as a source follower. It is called a floating diffusion because of that fact that its potential level will vary depending on the amount of charge present on the node. Source followers are used to preserve the linear relationship between light in, electrons generated and voltage output. The process begins by resetting the floating diffusion through a reset gate and reset drain which dictates the reset potential. This reset or zero signal level is converted to a voltage and immediately seen off chip which is processed as a reference level. The charge is then shifted from the last phase within the CCD and dumped onto the floating diffusion. The resulting change in potential is converted into a

PIXEL Pn+4 voltage and sensed off chip. The difference between the reference or reset level and the potential shift of the floating diffusion level determines the signal.

Figure 14: Floating Diffustion Readout Structure

CLOCK VOLTAGE TIMING WAVEFORMS

# V Related CCD Enhancing Technologies

### A) Color CCD Imaging

Silicon based CCD's are monochrome in nature. That is they have no natural ability to determine the varying amounts of red, green and blue (RGB) information presented to the pixels. What is used by the industry, however, are three techniques to extract color information for a given scene. A common problem to any of the color imaging techniques described is that the amount of information required triples.

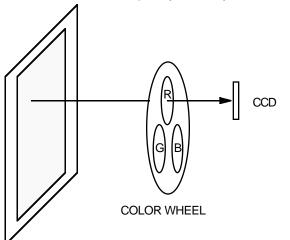

> 1) Color Sequential - A color image can be created using a CCD by taking three successive exposures while switching in optical filters having the desired RGB characteristics. The resulting image is then reconstructed off chip. The advantage to this technique is that resolution can remain that of the CCD itself. The disadvantage is that three exposures are required reducing frame times by more than a factor of three. The filter switching assembly also adds to the mechanical complexity of the system.

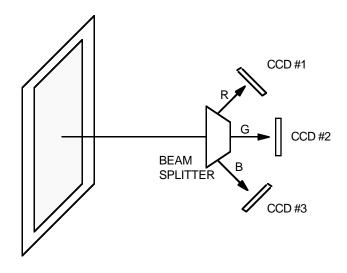

Figure 15: Color Sequential Capture

2) Three Chip Color - Instead of switching colors with a color filter wheel, three chip color systems use optics to split the scene onto three separate image planes. A CCD sensor and a corresponding color filter is placed in each of the three imaging planes. Color images can then be detected at once by synchronizing the outputs of the three CCD's thus reducing the frame rate back to that of a single sensor system. The disadvantage to such a system is that complexity is very high, effective data rate (bandwidth) has tripled and registration/calibration between sensors is difficult.

IMAGE SCENE

Figure 16: Three Chip Color Capture

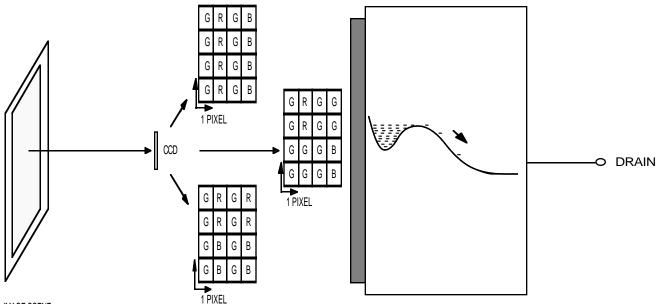

3) Integral Color Filter Arrays (CFA) -Instead of performing the color filtering off chip, one can place filters of the appropriate characteristics on chip. This approach can be performed during device fabrication using dyed (cyan, magenta, yellow) photoresists in The benefits of this various patterns. approach is considerably reduced system complexity. The major problem with this approach is that, unlike film, each pixel can only be patterned as one (primary color system RGB) or two colors (secondary color systems CMY) or a combination. Any choice results in the loss of information leading to reduced effective resolution and increased sampling (quantizing) artifacts. Another disadvantage is that off chip processing is required to "fill in" the missing color information between pixels thus increasing system complexity.

#### IMAGE SCENE

Figure 17: Integral Color Filter Array Patterns **B)** Anti-blooming

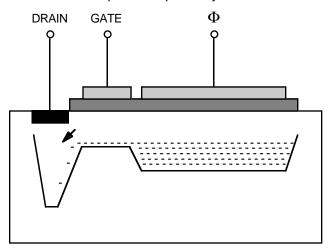

A problem with CCD's, unlike photographic film, is what happens when the device is over exposed. As mentioned earlier, electrons are created at a linearly proportional rate of exposure. If the size of the potential wells created in the CCD do not have the capacity to hold the integrated charge they will "bloom" or spill into adjacent pixels corrupting scene information. This "blooming" can be alleviated by building "antiblooming" or overflow drain structures within the device. Two common antiblooming structures are vertical overflow drains (VOD) and lateral overflow drains (LOD). A side benefit of incorporating an overflow drain is the ability to use that feature to create a means of electronic exposure or shutter control. Electronic exposure, which is much more accurate and reliable than mechanical shuttering. allows very versatile operation for systems or cameras.

1) VOD - VOD devices have built-in electrostatic potential barriers to the biased substrate. The barrier is designed to a level that is lower than the barriers between pixels. When collected charge exceeds this level it spills vertically through the silicon and swept away by the bias on the substrate. Disadvantages of this structure are device complexity, adding costs, and usually reduced well capacity leading to lower dynamic range.

2) LOD - One of the problems with VOD structures is that they have limited capacity in the amount of over exposure occurring. For the most demanding situations, a LOD structure is used. LOD is implemented on the surface of the silicon where the rest of the structures reside. In this case a barrier is created adjacent to the integrating pixels and charge spills into the drain laterally and swept off chip. The disadvantage of such a structure is reduced fill factor or aperture leading to reduced photo-responsivity.

Figure 19: Lateral Overflow Drain

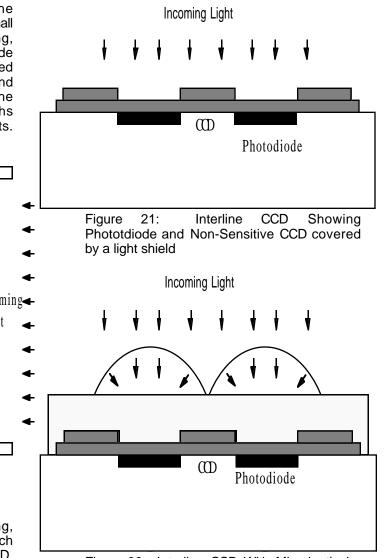

#### C) Silicon Thinning

As shown earlier, overlying films on the pixels absorb or reflect the light depending on wavelength. Electrons created at the very top surface (nominally ultraviolet and blue wavelengths) of the silicon are also lost due to recombination at the oxide-silicon interface. To increase the response of the sensor, the backside of the wafer is thinned to very small depths (~10-15 $\mu$ m). With the proper thinning, the CCD is then illuminated from the backside and UV and blue response is increased significantly. Thinning is restricted to FF and FT architectures without VOD structures. The difficulty in thinning the device to such depths leads to lower yields and higher costs. Handling becomes extremely difficult as well.

Figure 20: Thick and Thinned CCD

# **D) UV Enhancement Coatings**

To get around the difficulty of wafer thinning, UV sensitive phosphors are available which can be deposited directly on top of the CCD. These phosphors, which are transparent above  $0.45\mu m$ , absorb the UV and deep blue wavelengths and fluoresce at a longer wavelength. The only disadvantage of these coatings is the loss in spatial resolution due to light scattering.

# E) Microlenticular Arrays

IL and LOD architectures suffer from reduced aperture or optical fill-factor, as discussed earlier, resulting in lower sensitivity. То improve the sensitivity, microlenticular arrays are formed directly over each pixel. These arrays are tiny little lenses ("lenslets") which act to focus the light that would normally strike the non-photosensitive areas into those regions which are sensitive. Factors of improvements can be realized using this technique. Disadvantages include increased processing, uniformity of the lenses across the array and increased packaging difficulties.

Figure 22: Interline CCD With Microlenticular Arrays

# F) High Speed CCD's

To achieve the highest frame rate, various architectures and designs are employed. The limiting factor in high speed CCD's is designing the on-chip amplifier for the maximum speed without consuming a large amount of power. Increased power dissipation tends to cause localized heating in the chip which degrades uniformity. To overcome this problem, multiple outputs are used to partition the device into blocks so that data can be read in parallel. If two outputs are used then the effective data rate increases by a factor of two. The more parallelism used, the less bandwidth required for each output. Of course the problem arises in processing so many outputs. Because of the capacitance associated with the MOS based CCD device, high speed shift registers are sometimes limited by the off chip clock driver capability. Another problem associated with high speed CCD's is the inherent noise

coupling that occurs from system to device because of the capacitive nature of the CCD.